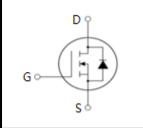

# **100V N-Channel DTMOS**

#### **FEATURES**

- Trench Power DTMOS Technology

- Low R<sub>DS(ON)</sub>

- Low Gate Charge

- Optimized for Fast-switching Applications

#### **APPLICATIONS**

- Synchronous Rectification in DC/DC and AC/DC Converters

- Isolated DC/DC Converters in Telecom and Industrial

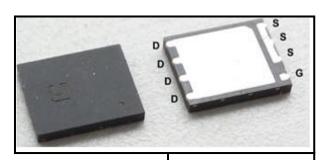

| Device Marking and Package Information |         |         |  |

|----------------------------------------|---------|---------|--|

| Device                                 | Package | Marking |  |

| TSG12N10AT                             | DFN5×6  | 12N10AT |  |

| <b>Absolute Maximum Ratings</b> $T_C = 25^{\circ}C$ , unless otherwise noted |                                   |          |      |  |

|------------------------------------------------------------------------------|-----------------------------------|----------|------|--|

| Parameter                                                                    | Symbol                            | Value    | Unit |  |

| Drain-Source Voltage (V <sub>GS</sub> = 0V)                                  | V <sub>DSS</sub>                  | 100      | V    |  |

| Continuous Drain Current                                                     | I <sub>D</sub>                    | 55       | Α    |  |

| Pulsed Drain Current (note1)                                                 | I <sub>DM</sub>                   | 220      | Α    |  |

| Gate-Source Voltage                                                          | V <sub>GSS</sub>                  | ±20      | V    |  |

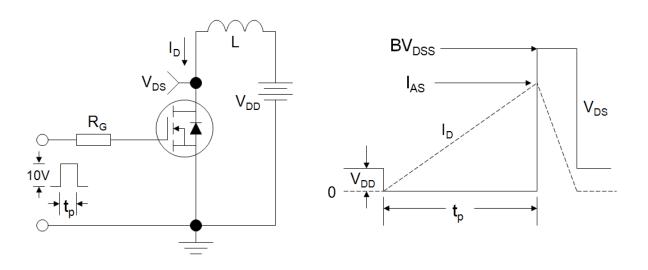

| Single Pulse Avalanche Energy (note2)                                        | E <sub>AS</sub>                   | 20       | mJ   |  |

| Avalanche Current (note1)                                                    | I <sub>As</sub>                   | 20       | Α    |  |

| Power Dissipation (T <sub>C</sub> = 25°C)                                    | P <sub>D</sub>                    | 56.5     | W    |  |

| Operating Junction and Storage Temperature Range                             | T <sub>J</sub> , T <sub>stg</sub> | -55~+150 | °C   |  |

| Thermal Resistance                      |                   |       |      |  |

|-----------------------------------------|-------------------|-------|------|--|

| Parameter                               | Symbol            | Value | Unit |  |

| Thermal Resistance, Junction-to-Case    | R <sub>thJC</sub> | 1.7   | 000  |  |

| Thermal Resistance, Junction-to-Ambient | R <sub>thJA</sub> | 50    | °C/W |  |

| Specifications T <sub>J</sub> = 25°C, unless otherwise noted |                       |                                                     |                                  |      |      |      |  |

|--------------------------------------------------------------|-----------------------|-----------------------------------------------------|----------------------------------|------|------|------|--|

| Parameter                                                    | Symbol                | Test Conditions                                     | Value                            |      |      | Unit |  |

|                                                              |                       |                                                     | Min.                             | Тур. | Max. |      |  |

| Static                                                       |                       |                                                     |                                  |      |      |      |  |

| Drain-Source Breakdown Voltage                               | $V_{(BR)DSS}$         | $V_{GS} = 0V, I_{D} = 250\mu A$                     | 100                              |      |      | V    |  |

| Zava Cata Valta va Brain Current                             | I <sub>DSS</sub>      | $V_{DS} = 95V, V_{GS} = 0V, T_{J} = 25^{\circ}C$    | $I_{GS} = 0V, T_J = 25^{\circ}C$ |      | 1    | μΑ   |  |

| Zero Gate Voltage Drain Current                              |                       | $V_{DS} = 95V, V_{GS} = 0V, T_{J} = 150^{\circ}C$   |                                  |      | 100  | μΑ   |  |

| Gate-Source Leakage                                          | I <sub>GSS</sub>      | $V_{GS} = \pm 20V$                                  |                                  |      | ±100 | nA   |  |

| Gate-Source Threshold Voltage                                | $V_{\rm GS(th)}$      | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$                | 1.1                              |      | 2.5  | V    |  |

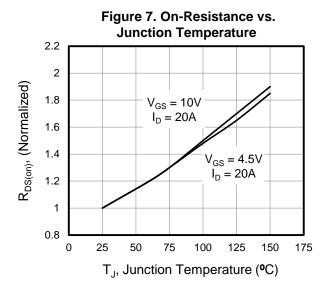

| Drain Course On Registeres (Note2)                           | D                     | $V_{GS} = 10V, I_D = 20A$                           |                                  | 9    | 12   |      |  |

| Drain-Source On-Resistance (Note3)                           | R <sub>DS(on)</sub>   | $V_{GS} = 4.5V, I_{D} = 20A$                        |                                  | 12.5 | 15.5 | mΩ   |  |

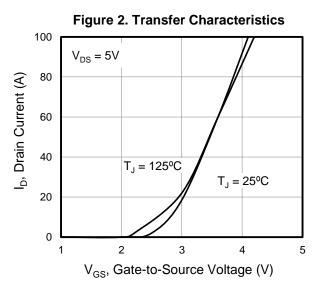

| Forward Transconductance (Note3)                             | g <sub>fs</sub>       | $V_{DS} = 5V, I_{D} = 20A$                          |                                  | 45   |      | S    |  |

| Dynamic                                                      |                       |                                                     |                                  |      |      |      |  |

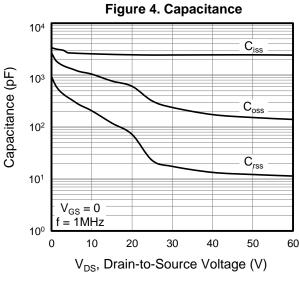

| Input Capacitance                                            | C <sub>iss</sub>      | V 0V                                                |                                  | 2455 |      | pF   |  |

| Output Capacitance                                           | C <sub>oss</sub>      | $V_{GS} = 0V,$<br>$V_{DS} = 50V,$                   |                                  | 153  |      |      |  |

| Reverse Transfer Capacitance                                 | C <sub>rss</sub>      | f = 1.0MHz                                          |                                  | 12   |      |      |  |

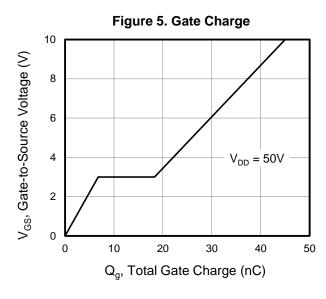

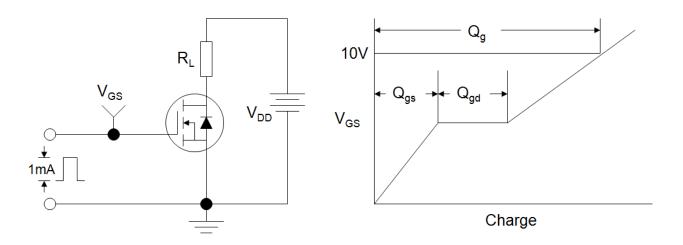

| T                                                            | Q <sub>g</sub> (10V)  |                                                     |                                  | 45   |      | nC   |  |

| Total Gate Charge                                            | Q <sub>g</sub> (4.5V) | $V_{DD} = 50V, I_{D} = 20A,$                        |                                  | 24   |      |      |  |

| Gate-Source Charge                                           | $Q_gs$                | $V_{GS} = 10V$                                      |                                  | 6.8  |      |      |  |

| Gate-Drain Charge                                            | $Q_{gd}$              |                                                     |                                  | 11.5 |      |      |  |

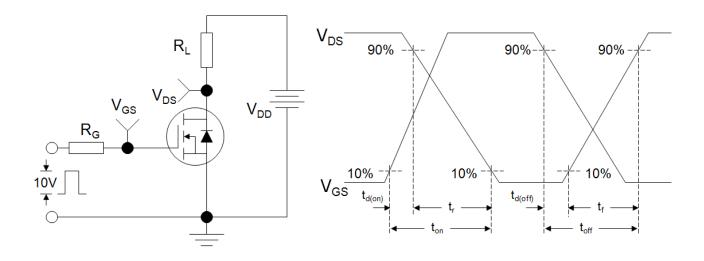

| Turn-on Delay Time                                           | t <sub>d(on)</sub>    |                                                     |                                  | 8    |      |      |  |

| Turn-on Rise Time                                            | t <sub>r</sub>        | $V_{DD} = 50V, I_{D} = 20A,$                        |                                  | 3    |      | ns   |  |

| Turn-off Delay Time                                          | t <sub>d(off)</sub>   | $R_G = 3\Omega$                                     |                                  | 25   |      |      |  |

| Turn-off Fall Time                                           | t <sub>f</sub>        |                                                     |                                  | 4    |      |      |  |

| Drain-Source Body Diode Characteri                           | stics                 |                                                     | •                                |      |      |      |  |

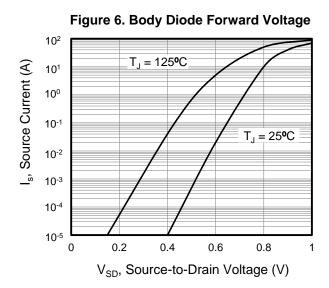

| Continuous Body Diode Current                                | Is                    |                                                     |                                  |      | 34   |      |  |

| Pulsed Diode Forward Current                                 | I <sub>SM</sub>       | $T_{\rm C} = 25^{\rm o}{\rm C}$                     |                                  |      | 102  | Α    |  |

| Body Diode Voltage                                           | $V_{SD}$              | $T_J = 25^{\circ}C$ , $I_{SD} = 1A$ , $V_{GS} = 0V$ |                                  | 0.72 | 1    | V    |  |

| Reverse Recovery Time                                        | t <sub>rr</sub>       | I <sub>F</sub> = 20A,                               |                                  | 27   |      | ns   |  |

| Reverse Recovery Charge                                      | Q <sub>rr</sub>       | $di_{F}/dt = 500A/\mu s$                            |                                  | 128  |      | nC   |  |

#### Notes

- 1. Repetitive Rating: Pulse Width limited by maximum junction temperature

- 2.  $I_{AS}$  = 20A,  $V_{DD}$  = 50V,  $R_{G}$  = 25 $\Omega$ , Starting  $T_{J}$  = 25 $^{\circ}$ C

- 3. Pulse Test: Pulse Width  $\leq$  300 $\mu$ s, Duty Cycle  $\leq$  1%

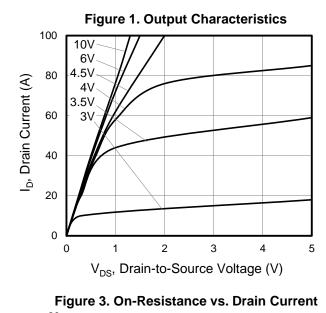

## **Typical Characteristics** $T_J = 25^{\circ}C$ , unless otherwise noted

$V_{GS} = 4.5V$   $V_{GS} = 4.5V$   $V_{GS} = 10V$   $V_{GS} = 10V$   $V_{GS} = 10V$   $V_{GS} = 25^{\circ}C$

I<sub>D</sub>, Drain Current (A)

20

25

0

0

## **Typical Characteristics** $T_J = 25^{\circ}\text{C}$ , unless otherwise noted

Figure 8. Threshold Voltage vs. **Junction Temperature** 1.2 1.1 V<sub>GS(th)</sub>, (Variance)  $I_{D} = 250 \mu A$ 1 0.9 8.0 0.7 0.6 0 -100 -50 50 100 150 200 T<sub>J</sub>, Junction Temperature (°C)

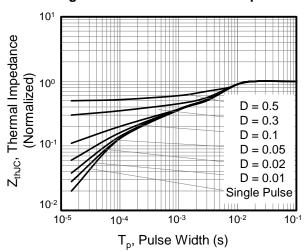

Figure 9. Transient Thermal Impedance

Figure A: Gate Charge Test Circuit and Waveform

Figure B: Resistive Switching Test Circuit and Waveform

Figure C: Unclamped Inductive Switching Test Circuit and Waveform

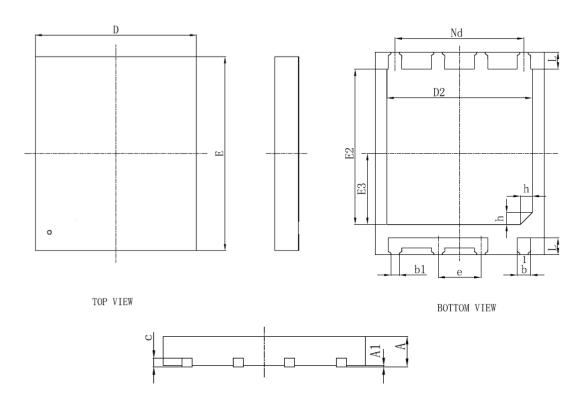

# DFN5×6

TOP VIEW

| SYMBOL | MILLIMETER |       |       |  |

|--------|------------|-------|-------|--|

| SIMDOL | MIN        | NOM   | MAX   |  |

| A      | 0.70       | 0.75  | 0.80  |  |

| A1     | 0          | 0.02  | 0.05  |  |

| b      | 0.35       | 0.40  | 0.45  |  |

| b1     | 0. 25REF   |       |       |  |

| С      | 0.18       | 0.203 | 0. 25 |  |

| D      | 4. 90      | 5. 00 | 5. 10 |  |

| D2     | 4. 20      | 4.30  | 4. 40 |  |

| SYMBOL | MILLIMETER |       |       |  |

|--------|------------|-------|-------|--|

| SIMBOL | MIN        | NOM   | MAX   |  |

| Nd     | 3. 81BSC   |       |       |  |

| e      | 1.27BSC    |       |       |  |

| Е      | 5. 90      | 6.00  | 6. 10 |  |

| E2     | 4. 50      | 4.60  | 4. 70 |  |

| E3     | 2.00       | 2. 10 | 2. 20 |  |

| L      | 0.45       | 0.50  | 0.55  |  |

| h      | 0.30       | 0.35  | 0.40  |  |

### **Disclaimer**

All product specifications and data are subject to change without notice.

For documents and material available from this datasheet, Wuxi Unigroup does not warrant or assume any legal liability or responsibility for the accuracy, completeness of any product or technology disclosed hereunder.

No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document or by any conduct of Wuxi Unigroup.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling Wuxi Unigroup products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Wuxi Unigroup for any damages arising or resulting from such use or sale.

Wuxi Unigroup disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Wuxi Unigroup's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

Wuxi Unigroup Microelectronics CO., LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

In the event that any or all Wuxi Unigroup products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

Information (including circuit diagrams and circuit parameters) herein is for example only. It is not guaranteed for volume production. Wuxi Unigroup believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.